# WН

## **CH567 Datasheet**

## Overview

CH567 is a high-performance 32-bit RISC reduced instruction set microcontroller, built-in 192KB FLASH memory, 32KB SRAM and 32KB DataFlash. The chip is integrated with two sets of independent high-speed USB2.0 master/slave controller, 4 groups of SD controllers, encryption algorithm modules, 4 groups of UART interfaces, 7 groups of PWMs, 3 groups of timers and other peripheral resources, which can be widely used for various embedded applications.

## Function

- Core:

- 32-bit RISC reduced instruction set core

- Highest frequency of 120MHz

- Memory:

-192KB-byte program memory, support write protection

- 32KB-byte SRAM

- 32KB-byte DataFlash

- Double USB2.0 high-speed receiver-transmitter (built-in PHY):

- High-speed Host / Device mode

- Support control/batch/interrupt/synchronous transmission

- Support double buffer PINT-PONG mechanism

- Support DMA

- 4 groups of independent SD controllers:

- Support single-wire, 4-wire, 8-wire communication mode

- Support SD/TF card, SDIO card and eMMC card, etc.

- Built-in FIFO

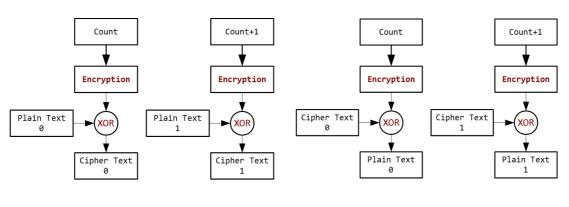

- Support AES and SM4 Algorithms

- Provide 8 encryption and decryption modes

- Support DMA

- Timer:

- 3 sets of 26-bit timers

Support functions of signal width sample / edge capture, PWM adjustable output and count

TMR1 and TMR2 support DMA

• Universal asynchronous receiver/transmitter (UART):

- 4 groups of independent UARTs, compatible

## with 16C550

- The highest baud rate is 6Mbps

- Built-in FIFO, multiple trigger levels

- PWMX:

- Expand 4 sets of PWM output

- Adjustable duty cycle

- SPI:

- 2 sets of SPI interfaces: one supports Master and Slave mode, and the other supports only Master mode

- Built-in FIFO

- SPI0 supports DMA

- LED screen interface:

- Support 1/2/4-channel data lines

- Built-in FIFO, support double buffer

- Support DMA

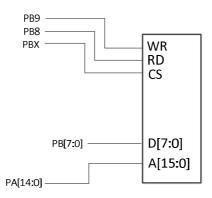

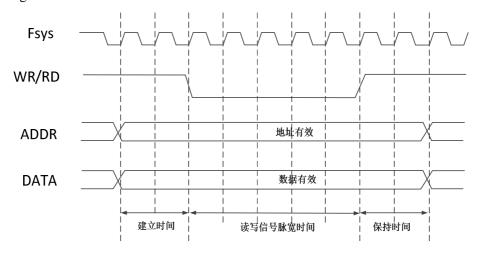

- Active parallel port:

- 8-bit data, 15-bit address bus

- Adjustable timing sequence

- Low power:

- Sleep mode

- Support some GPIOs or USB signal wake up

- General-purpose I/O port:

- 30 GPIOs

- 8 pins can be set level or edge interrupt

- Some pins have multiplexing and mapping functions

- ID Number of chip:

- Unique 64bit ID identification number

- Power supply:

- 3.0---3.6V (3.3V±10%)

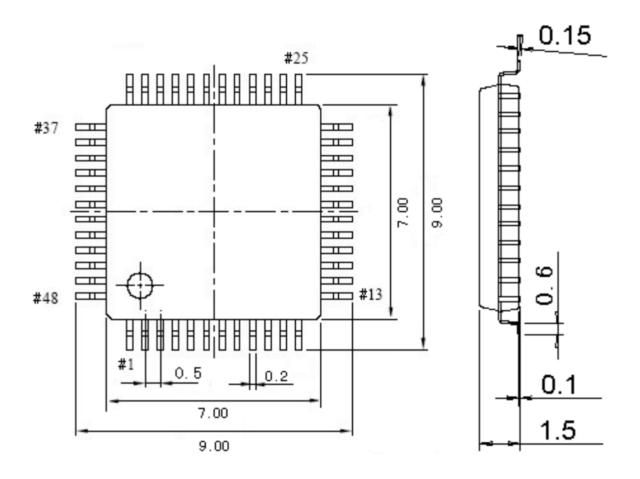

- Package: LQFP48

## Application

Security storage, home security, USB-related applications, monitoring, alarm systems, printers, scanners and other application control.

## **Chapter 1 Pin Information**

## **1.1 Pin Configuration**

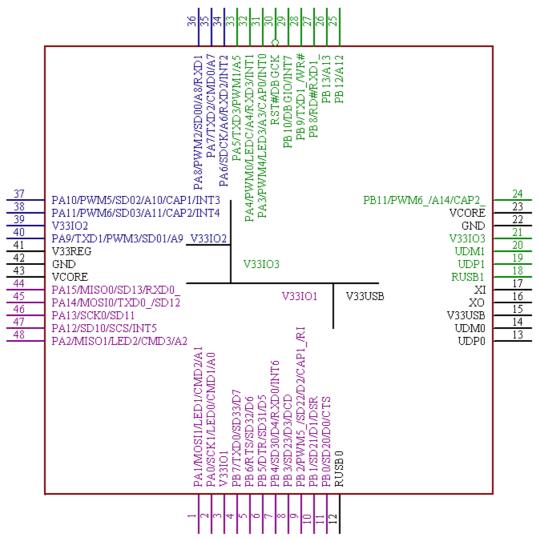

Figure 2-1 LQFP48 Package Pin Arrangement

## **1.2 Pin Description**

| Pin<br>No. | Pin<br>Name | Pin<br>Type | Main Function (after reset)/<br>Multiplexing Function and<br>Mapping | Function Description                                                                                                                                                                                                                                      |

|------------|-------------|-------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | PA1         | I/O         | PA1<br>/MOSI1/LED1/CMD2/A1                                           | <ul><li>PA1: General purpose bidirectional digital I/O pin.</li><li>MOSI1: SPI1 serial data pin, host output.</li><li>LED1: LED serial data line 1.</li><li>CMD2: SD2 controller command signal line.</li><li>A1: Parallel port address line 1.</li></ul> |

| 2          | PA0         | I/O         | PA0<br>/SCK1/LED0/CMD1/A0                                            | PA0: General purpose bidirectional digital I/O pin.<br>SCK1: SPI1 serial clock pin, host clock output.<br>LED0: LED serial data line 0.                                                                                                                   |

|     |        |       |                         | CMD1: SD1 controller command signal line.                     |

|-----|--------|-------|-------------------------|---------------------------------------------------------------|

|     |        |       |                         | A0: Parallel port address.                                    |

|     |        |       |                         | 1 set of 3.3V power supplies for peripherals, requires        |

| 3   | V33IO1 | Р     | V33IO1                  | an external 0.1uF capacitor.                                  |

|     |        |       |                         | PB7: General purpose bidirectional digital I/O pin.           |

|     |        |       | PB7                     | TXD0: UART0 serial data output.                               |

| 4   | PB7    | I/O   | /TXD0/SD33/D7           | SD33: SD3 controller data line 3.                             |

|     |        |       | /1200/5033/07           |                                                               |

|     |        |       |                         | D7: Parallel data line 7.                                     |

|     |        |       |                         | PB6: General purpose bidirectional digital I/O pin.           |

| ~   | DD (   | T/O   | PB6                     | RTS: MODEM output signal of UART0; request to                 |

| 5   | PB6    | I/O   | /RTS/SD32/D6            | send.                                                         |

|     |        |       |                         | SD32: SD3 controller data line 2.                             |

|     |        |       |                         | D6: Parallel data line 6.                                     |

|     |        |       |                         | PB5: General purpose bidirectional digital I/O pin.           |

|     |        |       | PB5                     | DTR: MODEM output signal of UART0; data                       |

| 6   | PB5    | I/O   | /DTR/SD31/D5            | terminal is ready.                                            |

|     |        |       |                         | SD31: SD3 controller data line 1.                             |

|     |        |       |                         | D5: Parallel data line 5.                                     |

|     |        |       |                         | PB4: General purpose bidirectional digital I/O pin.           |

|     |        |       | PB4                     | SD30: SD3 controller data line 0.                             |

| 7   | PB4    | I/O   | /SD30/D4/RXD0/INT6      | D4: Parallel data line 4.                                     |

|     |        |       | /SD30/D4/KAD0/IN10      | RXD0: UART0 serial data input.                                |

|     |        |       |                         | INT6: IO interrupt 6.                                         |

|     |        |       |                         | PB3: General purpose bidirectional digital I/O pin.           |

|     |        |       | DD2                     | SD23: SD2 controller data line 3.                             |

| 8   | PB3    | I/O   | PB3                     | D3: Parallel data line 3.                                     |

|     |        |       | /SD23/D3/DCD            | DCD: MODEM input signal of UART0; carrier                     |

|     |        |       |                         | detection.                                                    |

|     |        |       |                         | PB2: General purpose bidirectional digital I/O pin.           |

|     |        |       |                         | PWM5 : PWM5 function mapping.                                 |

|     |        | - 1 - | PB2                     | SD22: SD2 controller data line 2.                             |

| 9   | PB2    | I/O   | /PWM5 /SD22/D2/CAP1 /RI |                                                               |

|     |        |       |                         | CAP1 : CAP1 function mapping.                                 |

|     |        |       |                         | RI: MODEM input signal of UART0; ring indicator.              |

|     |        |       |                         | PB1: General purpose bidirectional digital I/O pin.           |

|     |        |       |                         | SD21: SD2 controller data line 1.                             |

| 10  | PB1    | I/O   | PB1                     | D1: Parallel data line 1.                                     |

|     |        | ~ ~   | /SD21/D1/DSR            | DTR: MODEM input signal of UART0; data device                 |

|     |        |       |                         | is ready.                                                     |

|     |        |       |                         | PB1: General purpose bidirectional digital I/O pin.           |

|     |        |       | PB0                     | SD20: SD2 controller data line 0.                             |

| 11  | PB0    | I/O   | /SD20/D0/CTS            | D0: Parallel data line 0.                                     |

|     |        |       | 15020/00/015            | CTS: MODEM input signal of UART0; clear to send.              |

|     |        |       |                         | It is required to be connected with a $12K\Omega$ resistor to |

| 12  | RUSB0  | I/O   | RUSB0                   |                                                               |

| 1.2 | LIDDO  | HOD   |                         | ground for USB0-PHY.                                          |

| 13  | UDP0   | USB   | UDP0(UD0+)              | USB0 bus D+ data line.                                        |

| 14  | UDM0   | USB   | UDM0(UD0-)              | USB0 bus D- data line.                                        |

| 15  | V33USB | P     | V33USB                  | USB0 peripheral power supply.                                 |

| 16  | XO     | I/O   | XO                      | Crystal oscillator inverted output                            |

Relevant information can be downloaded from the website: <u>www.wch.cn</u>

2

| 17 | XI     | Ι    | XI                   | Crystal oscillator input                                                                   |

|----|--------|------|----------------------|--------------------------------------------------------------------------------------------|

| 18 | RUSB1  | I/O  | RUSB1                | It is required to be connected with a $12K\Omega$ resistor to                              |

| 10 | LUDD1  | LICD |                      | ground for USB1-PHY.                                                                       |

| 19 | UDP1   | USB  | UDP1(UD1+)           | USB1 bus D+ data line.                                                                     |

| 20 | UDM1   | USB  | UDM1(UD1-)           | USB1 bus D- data line.                                                                     |

| 21 | V33IO3 | Р    | V33IO3               | 3 sets of 3.3V power supply for USB1 and peripheral, requires an external 0.1uF capacitor. |

| 22 | GND    | Р    | GND                  | Ground: common ground, 0V reference point.                                                 |

|    |        |      |                      | Core power supply, must be connected to VCORE                                              |

| 23 | VCORE  | Р    | VCORE                | and an external 0.1uF capacitor is required.                                               |

|    |        |      |                      | PB11: General purpose bidirectional digital I/O pin.                                       |

| 24 | PB11   | I/O  | PB11                 | PWM6_: PWM6 function mapping.                                                              |

| 24 | PDII   | 1/0  | /PWM6_/A14/CAP2_     | A14: Parallel port address line 14.                                                        |

|    |        |      |                      | CAP2_: CAP2 function mapping.                                                              |

| 25 | PB12   | I/O  | PB12                 | PB12: General purpose bidirectional digital I/O pin.                                       |

| 23 | PD12   | 1/0  | /A12                 | A12: Parallel port address line 12.                                                        |

| 26 | PB13   | I/O  | PB13                 | PB13: General purpose bidirectional digital I/O pin.                                       |

| 20 | PDIS   | 1/0  | /A13                 | A13: Parallel port address line 13.                                                        |

|    |        |      | PB8                  | PB9: General purpose bidirectional digital I/O pin.                                        |

| 27 | PB8    | I/O  | /RD#/RXD1            | RD#: Parallel port read control line.                                                      |

|    |        |      | /KD#/KADI_           | RXD1_: RXD pin mapping of UART1.                                                           |

|    |        |      | PB9                  | PB9: General purpose bidirectional digital I/O pin.                                        |

| 28 | PB9    | I/O  | /TXD1 /WR#           | TXD1_: TXD pin mapping of UART1.                                                           |

|    |        |      |                      | WR#: Parallel port write control line.                                                     |

|    |        |      |                      | PB10: General purpose bidirectional digital I/O pin.                                       |

| 29 | PB10   | I/O  | PB10                 | DBGIO: Data input and output port of simulation and                                        |

| 2) | 1010   | шO   | /DBGIO/INT7          | debugging interface.                                                                       |

|    |        |      |                      | INT7: IO interrupt 7.                                                                      |

|    |        |      |                      | RST#: External reset input pin, active low, built-in                                       |

| 30 | RST#   | Ι    | RST#                 | pull-up resistor.                                                                          |

| 50 | 10011  | 1    | /DBGCK               | DBGCK: Clock input port of simulation and                                                  |

|    |        |      |                      | debugging interface.                                                                       |

|    |        |      |                      | PA3: General purpose bidirectional digital I/O pin.                                        |

|    |        |      | PA3                  | PWM4: Pulse width modulation output channel 4.                                             |

| 31 | PA3    | I/O  | /PWM4/LED3/A3/CAP0   | LED3: LED serial data line 3.                                                              |

|    |        |      | /INT0                | A3: Parallel port address line 3.                                                          |

|    |        |      |                      | CAP0: Timer0 capture input pin.                                                            |

|    |        |      |                      | INTO: IO interrupt 0.                                                                      |

|    |        |      |                      | PA4: General purpose bidirectional digital I/O pin.                                        |

|    |        |      | PA4                  | PWM0: Pulse width modulation output channel 0.                                             |

| 32 | PA4    | I/O  | /PWM0/LEDC/A4/RXD3   | LEDC: LED serial data line.                                                                |

|    |        |      | /INT1                | A4: Parallel port address line 4.                                                          |

|    |        |      |                      | RXD3: UART3 serial data input.                                                             |

|    |        |      |                      | INT1: IO interrupt 1.                                                                      |

|    |        |      | PA5                  | PA5: General purpose bidirectional digital I/O pin.                                        |

| 33 | PA5    | I/O  | PA5<br>/TXD3/PWM1/A5 | TXD3: UART3 serial data output.                                                            |

|    |        |      | /IADJ/FWWWIVII/AJ    | PWM1: Pulse width modulation output channel 1.<br>A4: Parallel port address line 5.        |

| 34 | PA6    | I/O  | PA6                  | PA6: General purpose bidirectional digital I/O pin.                                        |

| 34 | rA0    | I/U  | rAu                  | 1 Ao. Ocherai purpose ordirectional digital I/O pln.                                       |

|    |                |            | /SDCK/A6/RXD2/INT2             | SDCK: SD controller clock line output.                                                    |

|----|----------------|------------|--------------------------------|-------------------------------------------------------------------------------------------|

|    |                |            |                                | A6: Parallel port address line 6.                                                         |

|    |                |            |                                | RXD2: UART2 serial data input.                                                            |

|    |                |            |                                | INT2: IO interrupt 2.                                                                     |

|    |                |            |                                | PA7: General purpose bidirectional digital I/O pin.                                       |

|    |                |            | PA7                            | TXD2: UART2 serial data output.                                                           |

| 35 | PA7            | I/O        | /TXD2/CMD0/A7                  | CMD0: SD0 controller command signal line.                                                 |

|    |                |            |                                | A7: Parallel port address line 7.                                                         |

|    |                |            |                                | PA8: General purpose bidirectional digital I/O pin.                                       |

|    |                |            |                                | PWM2: Pulse width modulation output channel 2.                                            |

| 36 | PA8            | I/O        | PA8                            | SDOO: SD0 controller data line 0.                                                         |

| 50 | 1710           | цО         | /PWM2/SD00/A8/RXD1             | A8: Parallel port address line 8.                                                         |

|    |                |            |                                | RXD1: UART1 serial data input.                                                            |

|    |                |            |                                |                                                                                           |

|    |                |            |                                | PA10: General purpose bidirectional digital I/O pin.                                      |

|    |                |            | PA10                           | PWM5: Pulse width modulation output channel 5.                                            |

| 37 | PA10           | I/O        | /PWM5/SD02/A10/CAP1            | SDO2: SD0 controller data line 2.                                                         |

|    |                |            | /INT3                          | A10: Parallel port address line 10.                                                       |

|    |                |            |                                | CAP1: Timer 1 capture input pin.                                                          |

|    |                |            |                                | INT3: IO interrupt 3.                                                                     |

|    |                |            |                                | PA11: General purpose bidirectional digital I/O pin.                                      |

|    |                |            | PA11                           | PWM6: Pulse width modulation output channel 6.                                            |

| 38 | PA11           | I/O        | /PWM6/SD03/A11/CAP2            | SD03: SD0 controller data line 3.                                                         |

| 50 | 1711           | ШО         | /I WIND/SD05/AII/CAI2<br>/INT4 | A11: Parallel port address line 11.                                                       |

|    |                |            | /11/14                         | CAP2: Timer2 capture input pin.                                                           |

|    |                |            |                                | INT4: IO interrupt 4.                                                                     |

| 20 | <b>W22IO2</b>  | р          | V22102                         | 2 sets of 3.3V power supplies for peripherals,                                            |

| 39 | V33IO2         | Р          | V33IO2                         | requires an external 0.1uF capacitor.                                                     |

|    |                |            |                                | PA9: General purpose bidirectional digital I/O pin.                                       |

|    |                |            | 210                            | TXD1: UART1 serial data output.                                                           |

| 40 | PA9            | I/O        | PA9                            | PWM3: Pulse width modulation output channel 3.                                            |

|    |                |            | TXD1/PWM3/SD01/A9              | SD01: SD0 controller data line 1.                                                         |

|    |                |            |                                | A9: Parallel port address line 9.                                                         |

|    |                |            |                                | Power supply voltage regulator input 3.3V power,                                          |

| 41 | V33REG         | Р          | V33REG                         | requires an external 0.1uF capacitor.                                                     |

| 42 | GND            | Р          | GND                            | Ground: common ground, 0V reference point.                                                |

|    | GILD           | -          | 0112                           | Core power supply output, and an external 3.3uF or                                        |

| 43 | VCORE          | Р          | VCORE                          | 10uF capacitor is required.                                                               |

|    |                |            |                                | PA15: General purpose bidirectional digital I/O pin.                                      |

|    |                |            | PA15                           | MIOS0: SPI0 serial data pin, host input/slave output.                                     |

| 44 | PA15           | I/O        | /MISO0/SD13/RXD0               | SD13: SD1 controller data line 3.                                                         |

|    |                |            | /1011500/5D15/KADU_            |                                                                                           |

|    |                |            |                                | RXD0_: RXD pin mapping of UART0.                                                          |

|    |                |            | DA 14                          | PA14: General purpose bidirectional digital I/O pin.                                      |

| 45 | PA14           | I/O        | PA14                           | MOSI0: SPI0 serial data pin, host output/slave input.                                     |

|    |                |            | /MOSI0/TXD0_/SD12              | TXD0_: TXD pin mapping of UART0.                                                          |

|    |                |            |                                | SD12: SD1 controller data line 2.                                                         |

|    |                |            | PA13                           | PA13: General purpose bidirectional digital I/O pin.                                      |

|    | <b>D</b> 1 1 2 |            |                                | SCK0: SPIO correl clock nin best output/clove input                                       |

| 46 | PA13           | I/O        | /SCK0/SD11                     | SCK0: SPI0 serial clock pin, host output/slave input.                                     |

| 46 | PA13<br>PA12   | I/O<br>I/O | /SCK0/SD11<br>PA12             | SD11: SD1 controller data line 1.<br>PA12: General purpose bidirectional digital I/O pin. |

Relevant information can be downloaded from the website: <u>www.wch.cn</u>

4

|    |      |     | /SD10/SCS/INT5                               | SD10: SD1 controller data line 0.                    |  |

|----|------|-----|----------------------------------------------|------------------------------------------------------|--|

|    |      |     | SCS: Chip selection input pin of SPI0 slave. |                                                      |  |

|    |      |     |                                              | INT5: IO interrupt 5.                                |  |

|    |      |     |                                              | PA2: General purpose bidirectional digital I/O pin.  |  |

| 10 | DA 2 | L/O |                                              | MISO1: SPI1 serial data pin, host input; serial data |  |

|    |      |     | PA2                                          | input and output pin in SPI1 simplex mode.           |  |

| 48 | PA2  | I/O | /MISO1/LED2/CMD3/A2                          | LED2: LED serial data line 2.                        |  |

|    |      |     |                                              | CMD3: SD3 controller command signal line.            |  |

|    |      |     |                                              | A2: Parallel port address line 2.                    |  |

#### ATTENTION:

(1). I: Input; O: Output; P: Power.

- (2) USB: USB signal.

- (3) The priority of multiplexing functions of the pins in the table are arranged in order from high to low (excluding the main function GPIO function)

Remarks :

In order to be compatible with the power supply system of external devices, CH567 will divide the power supply of peripherals for management and IOs and provide multiple sets of power pins. In the above pin description, the pins marked with different colors belong to different power domains, and the assignments are as follows:

Font color: Same as power supply V33REG/V33USB Font color: Same as power supply V33IO1 Font color: Same as power supply V33IO2 Font color: Same as power supply V33IO3

## **Chapter 2 System Structure and Memory**

## 2.1 System Structure

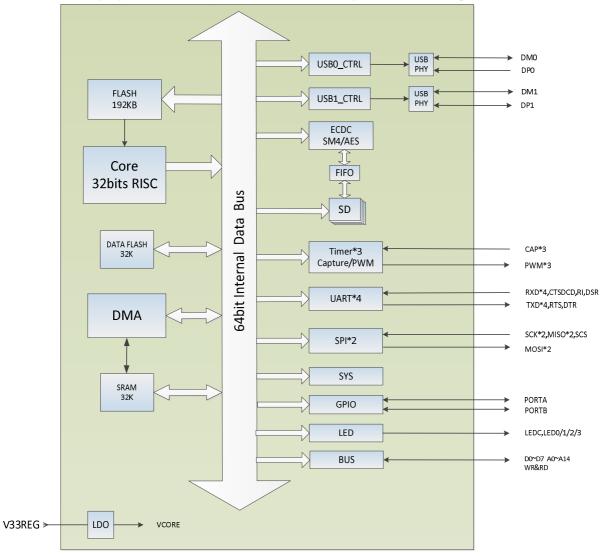

The following figure shows the system structure block diagram of CH567 chip.

Figure 2-1 CH567 Internal Structure Block Diagram

The CPU core, DMA arbitration controller, SRAM and various peripheral modules are mounted on the 64bit system bus of CH567. The DMA controller can be used for modules such as USB, SATA, SD, SPI0, LED and TIMER of peripherals.

## 2.2 Memory Mapping

CH567 includes a 4GB address space, and the memory map mainly contains several different areas, as shown in the figure below.

Figure 2-2 Memory Mapping

## 2.3 Memory Mapping

The address range of each memory mapping area is shown in the table below:

| Table 2-1 Memory Mapping Area Address |  |

|---------------------------------------|--|

|                                       |  |

| Address range           | Usage                                    | Description                 |

|-------------------------|------------------------------------------|-----------------------------|

| 0x0000 0000-0x0003 FFFF | On-chip non-volatile memory              | Flash memory (256KB)        |

| 0x0004 0000-0x001F FFFF | Reserved                                 | -                           |

| 0x0020 0000-0X0020 7FFF | On-chip SRAM, usually used to store data | 32KB                        |

| 0x0020 8000-0x003F FFFF | Reserved                                 | -                           |

| 0x0040 0000-0x0040 FFFF | Various peripherals                      | Multiple peripheral modules |

| 0x0041 0000-0x007F FFFF | Reserved                                 | -                           |

| 0x0080 0000-0x0080 7FFF | External system bus                      | 32KB                        |

| 0x0080 8000-0xFFFF 7FFF | Reserved                                 | -                           |

## 2.4 Peripheral Address Assignment

**Peripheral No.**

CH567 mainly contains the following peripherals. Each peripheral occupies a certain address space, and the actual access address of peripheral register is: base address + offset address. In the following chapters, the address of the register is described in detail. The following table shows the assignment of base address of each peripheral.

Table 2-2 Peripheral Base Address Assignment

Peripheral name Peripheral base address

| 1  | SYS   | 0x0040 1000 |

|----|-------|-------------|

| 2  | TMR0  | 0x0040 2000 |

| 3  | TMR1  | 0x0040 2400 |

| 4  | TMR2  | 0x0040 2800 |

| 5  | UART0 | 0x0040 3000 |

| 6  | UART1 | 0x0040 3400 |

| 7  | UART2 | 0x0040 3800 |

| 8  | UART3 | 0x0040 3C00 |

| 9  | SPI0  | 0x0040 4000 |

| 10 | SPI1  | 0x0040 4400 |

| 11 | PWMX  | 0x0040 5000 |

| 12 | LED   | 0x0040 6000 |

| 13 | USB0  | 0x0040 8000 |

| 14 | USB1  | 0x0040 9000 |

| 15 | SDC   | 0x0040 A000 |

| 16 | ECDC  | 0x0040 C400 |

The following table is the explanation of "Access" in the register description in the subsequent chapters:

| Abbreviation                                                 | Description                                              |

|--------------------------------------------------------------|----------------------------------------------------------|

| RF                                                           | The read value is fixed, which is not affected by reset. |

| RO                                                           | Read only.                                               |

| WO                                                           | Write only (the read value is 0 or invalid).             |

| RZ Read-only, automatically cleared after read operation.    |                                                          |

| WZ Write to clear.                                           |                                                          |

| RW Readable, writable.                                       |                                                          |

| RW1                                                          | Cleared by reading/writing 1.                            |

| WA Write-only (in safety mode), the read value is 0 or inval |                                                          |

| RWA Write in read/safety mode.                               |                                                          |

## **Chapter 3 System Control**

## **3.1 Power Control**

CH567 needs an external supply voltage of 3.3V. In the package pin description of Figure 1-1, multiple sets of power and ground are provided externally. Internal power management is provided with multi-power-domain grouping mode, which can connect different power systems according to the peripheral resources used.

After the system or power supply is reset, CH567 is in run state. When the CPU does not need to continue to run, or some functional modules do not need to be used, the clock or independent supply of these modules can be turned off, to reduce power consumption.

## **3.2 Reset Control**

CH567 supports 3 types of reset forms, namely power-on reset, external manual reset and internal software reset. System will reload the configuration information and reload the program code into the RAM buffer after reset. The load time is about 8.8mS.

The register R8\_GLOB\_RESET\_KEEP is only reset when power-on reset, and it is not affected by other types of reset.

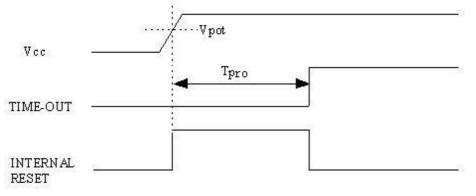

#### 3.2.1 Power-on Reset

When the power supply voltage is lower than the power-on reset threshold Vpot, CH567 will be reset. The figure below shows the power-on reset of CH567.

Figure 3-1 Power-on Reset

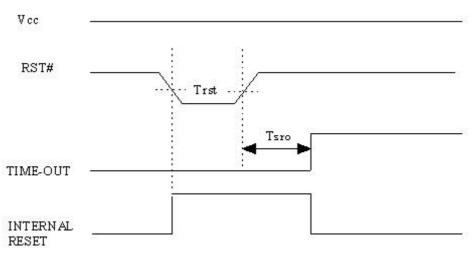

#### **3.2.2 External Manual Reset**

The external manual reset is generated by the low level applied to the RST# pin from the external. When the reset low level duration is greater than the minimum reset pulse width (Trst), the chip will be triggered to reset.

## 3.2.3 Internal Software Reset

The chip is provided with the internal software reset function, so that no external intervention is required to perform software reset in some specific situations. Set the bit RB\_SOFTWARE\_RESET of global reset configuration register (R8\_RST\_WDOG\_CTRL) to 1, to realize software reset. This bit will be automatically cleared.

#### 3.2.4 Reset Feature

Please refer to the timing parameter table in section 15.4 for reset parameters.

## **3.3 Register Description**

System control related register physical base address: 0x0040 1000

| Name               | Offset address | Description                         | Reset value |

|--------------------|----------------|-------------------------------------|-------------|

| R8_SAFE_ACCESS_SIG | 0x00           | Secure access flag register         | 8h00        |

| R8_CHIP_ID         | 0x01           | Chip ID register                    | 8h68        |

| R8_SAFE_ACCESS_ID  | 0x02           | Secure access ID register           | 8h02        |

| R8_GLOB_ROM_CFG    | 0x04           | ROM configuration register          | 8h80        |

| R8_RST_BOOT_STAT   | 0x05           | BOOT status register                | 8hC1        |

| R8_RST_WDOG_CTRL   | 0x06           | Reset register                      | 8h00        |

| R8_GLOB_RESET_KEEP | 0x07           | Reset keep register                 | 8h00        |

| R8_SLP_WAKE_CTRL   | 0x0E           | Wake-up control register            | 8h00        |

| R8_SLP_POWER_CTRL  | 0x0F           | Low-power power management register | 8h00        |

| Table 3-1 | List of Clock ar | nd CPU Control | Related Registers |

|-----------|------------------|----------------|-------------------|

|           |                  |                |                   |

Security access flag register (R8\_SAFE\_ACCESS\_SIG):

| Bit   | Name               | Access | Description                                                                                                                                                                                                                                                                 | Reset<br>value |

|-------|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| [7:0] | R8_SAFE_ACCESS_SIG | WO     | Secure access flag register.<br>Some registers (access attribute is RWA) are<br>protected registers, read/write operation can<br>be performed only after entering the secure<br>access mode. Write 0x57 first and then 0xA8<br>to this register, to enter the secure access | 00h            |

|       |                   |    | mode. And the time is limited to about 110 main clock cycles (Tsys), and it will be automatically protected beyond the time limit. |   |

|-------|-------------------|----|------------------------------------------------------------------------------------------------------------------------------------|---|

| [6:4] | RB_SAFE_ACC_TIMER | RO | Secure access time, fixed at 128 Tsys                                                                                              | 0 |

| [1:0] | RB_SAFE_ACC_MODE  | RO | Current secure access mode status:<br>11: Secure mode, registers with RWA attribute<br>can be accessed;<br>Other: Non-secure mode; | 0 |

Chip ID register (R8\_CHIP\_ID)

| Bit   | Name       | Access | Description                                    | Reset<br>value |

|-------|------------|--------|------------------------------------------------|----------------|

| [7:0] | R8_CHIP_ID | RF     | Fixed value of 67h, used to identify the chip. | 67h            |

## Secure access ID register (R8\_SAFE\_ACCESS\_ID):

| Bit   | Name              | Access | Description         | Reset<br>value |

|-------|-------------------|--------|---------------------|----------------|

| [7:0] | R8_SAFE_ACCESS_ID | RF     | Fixed value of 02h. | 02h            |

## ROM configuration register (R8\_GLOB\_ROM\_CFG):

| Bit   | Name           | Access | Description                                       | Reset<br>value |

|-------|----------------|--------|---------------------------------------------------|----------------|

| [7:4] | Reserved       | RWA    | Reserved, must write 01b to [7:6], the read is 0. | 0000b          |

|       |                |        | Flash ROM code and data area erase/program        |                |

| 3     | RB ROM CODE WE | RWA    | enable bit:                                       | 0              |

|       |                |        | 1: Programmable/erasable;                         |                |

|       |                |        | 0: Write protection                               |                |

|       |                |        | Flash ROM data area erase/program enable bit:     |                |

| 2     | RB_ROM_DATA_WE | RWA    | 1: Programmable/erasable;                         | 0              |

|       |                |        | 0: Write protection.                              |                |

|       |                |        | Code RAM area write enable bit:                   |                |

| 1     | RB_CODE_RAM_WE | RWA    | 1: Write enabled;                                 | 0              |

|       |                |        | 0: Write protection.                              |                |

|       |                |        | External programmer read Flash ROM enable         |                |

| 0     | DD DOM EVT DE  | RO     | bit:                                              | 0              |

| 0     | RB_ROM_EXT_RE  | ĸŪ     | 1: Read enabled;                                  | 0              |

|       |                |        | 0: Read protection.                               |                |

## BOOT status register (R8\_RST\_BOOT\_STAT)

| Bit   | Name            | Access | Description                          | Reset<br>value |

|-------|-----------------|--------|--------------------------------------|----------------|

| [7:6] | Reserved        | RO     | Reserved.                            | 11b            |

|       |                 |        | Boot loader status:                  |                |

| 5     | RB_BOOT_LOADER  | RO     | 1: Boot loader status (Boot-Loader); | 0              |

|       |                 |        | 0: User program status.              |                |

|       |                 |        | Debugging enable control bit:        |                |

| 4     | RB_CFG_DEBUG_EN | RO     | 1: Enable;                           | 0              |

|       |                 |        | 0: Disable.                          |                |

Relevant information can be downloaded from the website: www.wch.cn

11

| 3     | RB_CFG_BOOT_EN  | RO | Boot program enable control bit:<br>1: Enable;<br>0: Disable.                                  | 0 |

|-------|-----------------|----|------------------------------------------------------------------------------------------------|---|

| 2     | RB_CFG_RESET_EN | RO | External reset enable control bit:<br>1: External input low-level signal reset;<br>0: Disable. | 0 |

| [1:0] | RB_RESET_FLAG   | RO | Last reset flag, as shown in Table 3-2.                                                        | 1 |

## Table 3-2 Last Reset Flag Description

| RB_RESET_FLAG | Reset Flag Description                                                              |

|---------------|-------------------------------------------------------------------------------------|

| 00b           | Software reset, source: RB_SOFTWARE_RESET=1 and RB_BOOT_LOADER=0.                   |

| 01b           | Power on reset, source: Chip operating voltage is lower than the threshold voltage. |

| 11b           | Manual reset, source: RST# pin input low level.                                     |

#### Reset register (R8\_RST\_WDOG\_CTRL)

| Bit   | Name              | Access    | Description                                                                       | Reset<br>value |

|-------|-------------------|-----------|-----------------------------------------------------------------------------------|----------------|

| [7:1] | Reserved          | RO        | Reserved, must write 01b to [7:6].                                                | 00h            |

| 0     | RB_SOFTWARE_RESET | WA/<br>WZ | System software reset; cleared automatically:<br>1: System reset;<br>0: No action | 0              |

## Reset keep register (R8\_GLOB\_RESET\_KEEP)

| Bit   | Name               | Access | Description                                                                                                              | Reset<br>value |

|-------|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------|----------------|

| [7:0] | R8_GLOB_RESET_KEEP | RW     | Reset keep register. The value of this register is<br>not affected by manual reset, software reset or<br>watchdog reset. | 00h            |

## Wake-up control register (R8\_SLP\_WAKE\_CTRL)

| Bit   | Name             | Access | Description                                                        | Reset<br>value |

|-------|------------------|--------|--------------------------------------------------------------------|----------------|

| [7:5] | Reserved         | RO     | Reserved.                                                          | 0              |

| 4     | RB_SLP_GPIO_WAKE | RWA    | GPIO port wake-up enable control bit:<br>1: Enable;<br>0: Disable. | 0              |

| [3:2] | Reserved         | RO     | Reserved.                                                          | 0              |

| 1     | RB_SLP_USB1_WAKE | RWA    | USB1 wake-up enable control bit:<br>1: Enable;<br>0: Disable.      | 0              |

| 0     | RB_SLP_USB0_WAKE | RWA    | USB0 wake-up enable control bit:<br>1: Enable;<br>0: Disable.      | 0              |

## Low-power power management register (R8\_SLP\_POWER\_CTRL)

| Bit | Name           | Access | Description                               | Reset<br>value |

|-----|----------------|--------|-------------------------------------------|----------------|

| 7   | RB_SLP_STANDBY | RWA    | Low-power mode control bit; automatically | 0              |

|       |                   |     | cleared after entering the mode: |   |

|-------|-------------------|-----|----------------------------------|---|

|       |                   |     | 1: Request core low power;       |   |

|       |                   |     | 0: No action.                    |   |

| [6:2] | Reserved          | RO  | Reserved.                        | 0 |

|       |                   |     | USB1 power control bit:          |   |

| 1     | RB_SLP_USB1_PWRDN | RWA | 1: Power off;                    | 0 |

|       |                   |     | 0: Power on normally.            |   |

|       |                   |     | USB0 power control bit:          |   |

| 0     | RB_SLP_USB0_PWRDN | RWA | 1: Power off;                    | 0 |

|       |                   |     | 0: Power on normally.            |   |

## 3.4 Low Power Mode and Wake-up

In the low-power state (RB\_SLP\_STANDBY bit is set to 1), the PLL will stop working, the internal clock of CH567 will be suspended, the CPU will not work or respond to any interrupts. However, if CPU starts working after waking up, and it is found that the wake-up event is also an interrupt event (for example, a certain GPIO wakes up and GPIO interrupt is generated), it will be treated as an interrupt.

In order to reduce power, the physical PHY module (such as USB) that is not used during the low power period shall be turned off before entering the low power state. Set RB\_SLP\_USB0\_PWRDN bit to 1, and set RB\_SLP\_USB1\_PWRDN bit to 1. In addition, GPIO pins cannot be in floating state, and need to be set to output state or input state with an external fixed level. If there is no external input with a fixed level, they need to be set to input state under internal pull-down mode.

In low power mode, CH567 only supports the wake-up of part of GPIO or USB, please refer to R8 SLP WAKE CTRL register.

There are 8 GPIO pins that support wake-up, which are 8 pins that support GPIO interrupt. GPIO wake-up event source is the same as the GPIO interrupt event source, but only triggered by level (R8\_GPIO\_INT\_MODE is not required). When the bit corresponding to R8\_GPIO\_INT\_POLAR is 0, a low level occurs on GPIO pin, then it will wake up. When the bit corresponding to R8\_GPIO\_INT\_POLAR is 1, a high level occurs on GPIO pin, then it will wake up.

Take GPIO port PA3 wake-up as an example, the configuration is as follows:

RB\_GPIO\_PA3\_IP=0;

RB\_GPIO\_PA3\_IE=1;

RB SLP GPIO WAKE=1;

When a low level occurs at PA3 port, a wake-up event will be generated. After CH567 exits the low-power mode, it will trigger the GPIO interrupt of PA3 port.

## **Chapter 4 Clock Control**

## 4.1 Clock Block Diagram

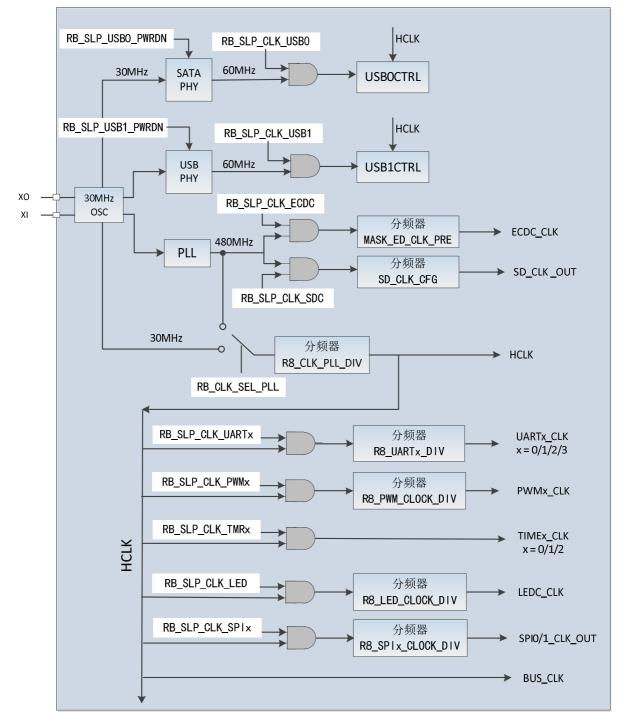

The internal clock structure of CH567 is shown in the figure below:

Figure 4-1 Clock Structure Block Diagram

After the external clock is sent to CH567, it will be connected to USB-PHY to generate the clock frequency required by USB controller, and generate the frequency multiplication clock of 480MHz through the PLL module. Get the clock frequency of 30MHz or 480MHz before frequency division through the clock source selection control bit (RB CLK SEL PLL). At this time, the clock frequency will get the system

clock Fsys (HCLK) through the frequency divider (R8\_CLK\_PLL\_DIV), namely the main clock of CPU, with a range of 2MHz-120MHz.

Each peripheral module clock has a corresponding clock register control bit, which can be turned on or off independently. In order to reduce the power of chip, you can turn off the function module clocks that are not used.

## **4.2 Register Description**

Clock control related register physical base address: 0x0040 1000

| 8               |                |                                   |             |  |

|-----------------|----------------|-----------------------------------|-------------|--|

| Name            | Offset address | Description                       | Reset value |  |

| R8_CLK_PLL_DIV  | 0x08           | PLL output clock divider register | 8h42        |  |

| R8_CLK_CFG_CTRL | 0x0A           | Clock configuration register      | 8h80        |  |

| R8_SLP_CLK_OFF0 | 0x0C           | Sleep control register 0          | 8h00        |  |

| R8_SLP_CLK_OFF1 | 0x0D           | Sleep control register 1          | 8h00        |  |

Table 4-1 List of Clock Control Related Registers

#### PLL output clock divider register (R8\_CLK\_PLL\_DIV)

| Bit   | Name           | Access | Description                                                                      | Reset<br>value |

|-------|----------------|--------|----------------------------------------------------------------------------------|----------------|

| [7:0] | R8_CLK_PLL_DIV | RWA    | The lower 4 bits are valid, must write 01b to [7:6], and the minimum value is 2. | 8h42           |

#### Clock configuration register (R8\_CLK\_CFG\_CTRL)

| Bit   | Name             | Access | Description                              | Reset<br>value |

|-------|------------------|--------|------------------------------------------|----------------|

| [7:2] | Reserved         | RWA    | Reserved, must write 01b to [7:6].       | 100000b        |

|       |                  |        | Clock source selection:                  |                |

| 1     | RB_CLK_SEL_PLL   | RWA    | 1:PLL 480MHz;                            | 0              |

|       |                  |        | 0: External crystal oscillator of 30MHz. |                |

|       |                  |        | PLL sleep control bit:                   |                |

| 0     | RB_CLK_PLL_SLEEP | RWA    | 1: PLL sleep;                            | 0              |

|       |                  |        | 0: PLL works normally.                   |                |

#### Sleep control register 0 (R8 SLP CLK OFF0)

| Bit | Name             | Access | Description                                                                               | Reset<br>value |

|-----|------------------|--------|-------------------------------------------------------------------------------------------|----------------|

| 7   | RB_SLP_CLK_UART3 | RWA    | UART3 clock control bit:<br>1: UART3 clock is turned off;<br>0: UART3 clock is turned on. | 0              |

| 6   | RB_SLP_CLK_UART2 | RWA    | UART2 clock control bit:<br>1: UART2 clock is turned off;<br>0: UART2 clock is turned on. | 0              |

| 5   | RB_SLP_CLK_UART1 | RWA    | UART1 clock control bit:<br>1: UART1 clock is turned off;<br>0: UART1 clock is turned on. | 0              |

| 4   | RB_SLP_CLK_UART0 | RWA    | UART0 clock control bit:<br>1: UART0 clock is turned off;                                 | 0              |

|   |                 |     | 0: UART0 clock is turned on.   |   |

|---|-----------------|-----|--------------------------------|---|

|   |                 |     | PWM clock control bit:         |   |

| 3 | RB_SLP_CLK_PWMX | RWA | 1: PWM clock is turned off;    | 0 |

|   |                 |     | 1: PWM clock is turned on.     |   |

|   |                 |     | TIMER2 clock control bit:      |   |

| 2 | RB_SLP_CLK_TMR2 | RWA | 1: TIMER2 clock is turned off; | 0 |

|   |                 |     | 0: TIMER2 clock is turned on.  |   |

|   |                 |     | TIMER1 clock control bit:      |   |

| 1 | RB_SLP_CLK_TMR1 | RWA | 1: TIMER1 clock is turned off; | 0 |

|   |                 |     | 0: TIMER1 clock is turned on.  |   |

|   |                 |     | TIMER0 clock control bit:      |   |

| 0 | RB_SLP_CLK_TMR0 | RWA | 1: TIMER0 clock is turned off; | 0 |

|   |                 |     | 0: TIMER0 clock is turned on.  |   |

Sleep control register 1 (R8\_SLP\_CLK\_OFF1)

| Bit | Name            | Access | Description                                                                                                                                               | Reset<br>value |

|-----|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 7   | RB_SLP_CLK_ECDC | RWA    | <ul><li>ECDC (encryption/decryption module) clock</li><li>control bit:</li><li>1: ECDC clock is turned off;</li><li>1: ECDC clock is turned on.</li></ul> | 0              |

| 6   | Reserved        | RO     | Reserved.                                                                                                                                                 | 0              |

| 5   | RB_SLP_CLK_USB1 | RWA    | USB clock control bit:<br>1: USB clock is turned off;<br>1: USB clock is turned on.                                                                       | 0              |

| 4   | RB_SLP_CLK_USB0 | RWA    | USB0 clock control bit:<br>1: USB0 clock is turned off;<br>0: USB0 clock is turned on.                                                                    | 0              |

| 3   | RB_SLP_CLK_LED  | RWA    | LEDC clock control bit:<br>1: LEDC clock is turned off;<br>1: LEDC clock is turned on.                                                                    | 0              |

| 2   | RB_SLP_CLK_SDC  | RWA    | <ul><li>SDC clock control bit:</li><li>1: SDC clock is turned off;</li><li>1: SDC clock is turned on.</li></ul>                                           | 0              |

| 1   | RB_SLP_CLK_SPI1 | RWA    | <ul><li>SPI1 clock control bit:</li><li>1: SPI1 clock is turned off;</li><li>0: SPI1 clock is turned on.</li></ul>                                        | 0              |

| 0   | RB_SLP_CLK_SPI0 | RWA    | <ul><li>SPI0 clock control bit:</li><li>1: SPI0 clock is turned off;</li><li>0: SPI0 clock is turned on.</li></ul>                                        | 0              |

## 4.3 System Clock Configuration

External crystal oscillator clock: Fosc = 30MHz;

PLL frequency multiplication clock: Fpll = 480MHz;

1. Select PLL clock source: Fsrc = RB CLK SEL PLL? PLL FREQ : OSC FREQ;

2. System clock calculation: Fsys = Fsrc / R8\_CLK\_PLL\_DIV, (2MHz - 120MHz).

When the system is powered on, 30MHz is selected as the PLL clock source by default, the frequency division factor is 2, and the default main frequency is 15MHz.

## Chapter 5 General purpose and Multiplexing I/O

## 5.1 Introduction to GPIO

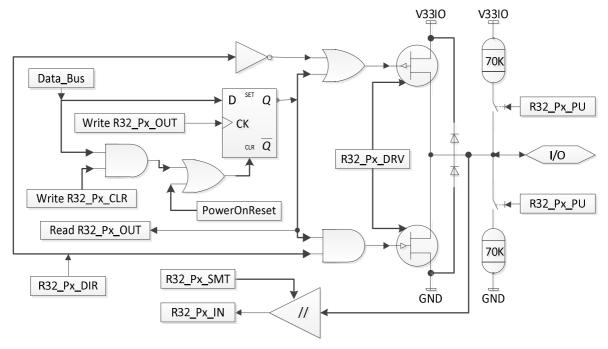

The system is equipped with 2 sets of GPIO ports of PA and PB, with a total of 30 general purpose input/output pins, and some pins have multiplexing and mapping functions. Each GPIO port has a 32-bit direction configuration register (R32\_Px\_DIR), a 32-bit data input register (R32\_Px\_PIN), a 32-bit data clear register (R32\_Px\_CLR), a 32-bit pull-up configuration register (R32\_Px\_PU), a 32-bit open drain output and input pull-down configuration register (R32\_Px\_PD), a 32-bit I/O drive capability configuration register (R32\_Px\_DRV) and a 32-bit Schmitt trigger enable configuration register (R32\_Px\_SMT).

In the PA port, the PA[0]-PA[15] bits are valid, corresponding to the 16 GPIO pins on the chip. In the PB port, the PB[0]-PB[13] bits are valid, corresponding to the 14 GPIO pins on the chip. Among them, 8 GPIO ports have interrupt function and can realize sleep and wake-up function.

Each I/O port bit can be freely programmed, but the I/O port register must be accessed by 8-bit, 16-bit or 32-bit words. If the multiplexing function of pin is not enabled, it will be used as a general-purpose I/O port.

The following figure is a block diagram of the internal structure of GPIO:

Figure 5-1 IO Internal Structure Block Diagram

## **5.2 Register Description**

GPIO related register physical base address: 0x0040 1000

| Name               | Offset address | Description                          | Reset value |

|--------------------|----------------|--------------------------------------|-------------|

| R8_GPIO_INT_STATUS | 0x1C           | GPIO interrupt flag register         | 8h00        |

| R8_GPIO_INT_ENABLE | 0x1D           | GPIO interrupt enable register       | 8h00        |

| R8_GPIO_INT_MODE   | 0x1E           | GPIO interrupt trigger mode register | 8h00        |

| R8_GPIO_INT_POLAR  | 0x1F           | GPIO interrupt polarity register     | 8h00        |

Table 5-1 List of GPIO Related Registers

| R32_PA_DIR  | 0x40 | PA port direction setting register                                   | 32h0000 0000 |

|-------------|------|----------------------------------------------------------------------|--------------|

| R32_PA_PIN  | 0x44 | PA port data input register                                          | 32hxxxx xxxx |

| R32_PA_OUT  | 0x48 | PA port data output register                                         | 32h0000 0000 |

| R32_PA_CLR  | 0x4C | PA port output clear register                                        | 32h0000 0000 |

| R32_PA_PU   | 0x50 | PA port pull-up enable register                                      | 32h0000 0000 |

| R32_PA_PD   | 0x54 | PA port open-drain output and input pull-down configuration register | 32h0000 0000 |

| R32_PA_DRV  | 0x58 | PA port drive capability configuration register                      | 32h0000 0000 |

| R32_PA_SMT  | 0x5C | PA port Schmitt trigger enable configuration register                | 32h0000 0000 |

| R32_PB_DIR  | 0x60 | PB port direction setting register                                   | 32h0000 0000 |

| R32_PB_PIN  | 0x64 | PB port data input register                                          | 32hxxxx 8000 |

| R32_PB_OUT  | 0x68 | PB port data output register                                         | 32h0000 0000 |

| R32_PB_CLR  | 0x6C | PB port output clear register                                        | 32h0000 0000 |

| R32_PB_PU   | 0x70 | PB port pull-up configuration register                               | 32h0000 0000 |

| R32_PB_PD   | 0x74 | PB port open-drain output and input pull-down configuration register | 32h0000 0000 |

| R32_PB_DRV  | 0x78 | PB port drive capability configuration register                      | 32h0000 0000 |

| R32_PB_SMT  | 0x7C | PB port Schmitt trigger enable configuration register                | 32h0000 0000 |

| R8_PORT_PIN | 0x12 | Multiplexing and remapping configuration register                    | 8h00         |

## GPIO interrupt flag register (R8\_GPIO\_INT\_STATUS)

| Bit | Name            | Access | Description                                        | Reset<br>value |

|-----|-----------------|--------|----------------------------------------------------|----------------|

|     |                 |        | PB10 pin interrupt flag bit, cleared by writing 1: |                |

| 7   | RB_GPIO_PB10_IS | RW1    | 1: An interrupt is generated;                      | 0              |

|     |                 |        | 0: No interrupt is generated.                      |                |

|     |                 |        | PB4 pin interrupt flag bit, cleared by writing 1:  |                |

| 6   | RB_GPIO_PB4_IS  | RW1    | 1: An interrupt is generated;                      | 0              |

|     |                 |        | 0: No interrupt is generated.                      |                |

|     |                 |        | PA12 pin interrupt flag bit, cleared by writing 1: |                |

| 5   | RB_GPIO_PA12_IS | RW1    | 1: An interrupt is generated;                      | 0              |

|     |                 |        | 0: No interrupt is generated.                      |                |

|     |                 |        | PA11 pin interrupt flag bit, cleared by writing 1: |                |

| 4   | RB_GPIO_PA11_IS | RW1    | 1: An interrupt is generated;                      | 0              |

|     |                 |        | 0: No interrupt is generated.                      |                |

|     |                 |        | PA10 pin interrupt flag bit, cleared by writing 1: |                |

| 3   | RB_GPIO_PA10_IS | RW1    | 1: An interrupt is generated;                      | 0              |

|     |                 |        | 0: No interrupt is generated.                      |                |

|     |                 |        | PA6 pin interrupt flag bit, cleared by writing 1:  |                |

| 2   | RB_GPIO_PA6_IS  | RW1    | 1: An interrupt is generated;                      | 0              |

|     |                 |        | 0: No interrupt is generated.                      |                |

| 1   |                 | DW1    | PA4 pin interrupt flag bit, cleared by writing 1:  | 0              |

| 1   | RB_GPIO_PA4_IS  | RW1    | 1: An interrupt is generated;                      | 0              |

|   |                |     | 0: No interrupt is generated.                   |   |

|---|----------------|-----|-------------------------------------------------|---|

|   |                |     | PA3 pin interrupt flag bit, clear by writing 1: |   |

| 0 | RB_GPIO_PA3_IS | RW1 | 1: An interrupt is generated;                   | 0 |

|   |                |     | 0: No interrupt is generated.                   |   |

## GPIO interrupt enable register (R8\_GPIO\_INT\_ENABLE)

| Bit | Name            | Access | Description                             | Reset<br>value |

|-----|-----------------|--------|-----------------------------------------|----------------|

|     |                 |        | PB10 pin interrupt enable bit:          |                |

| 7   | RB_GPIO_PB10_IE | RW     | 1: Enable the corresponding interrupt;  | 0              |

|     |                 |        | 0: Disable the corresponding interrupt. |                |

|     |                 |        | PB4 pin interrupt enable bit:           |                |

| 6   | RB_GPIO_PB4_IE  | RW     | 1: Enable the corresponding interrupt;  | 0              |

|     |                 |        | 0: Disable the corresponding interrupt. |                |

|     |                 |        | PA12 pin interrupt enable bit:          |                |

| 5   | RB_GPIO_PA12_IE | RW     | 1: Enable the corresponding interrupt;  | 0              |

|     |                 |        | 0: Disable the corresponding interrupt. |                |

|     |                 |        | PA11 pin interrupt enable bit:          |                |

| 4   | RB_GPIO_PA11_IE | RW     | 1: Enable the corresponding interrupt;  | 0              |

|     |                 |        | 0: Disable the corresponding interrupt. |                |

|     |                 |        | PA10 pin interrupt enable bit:          |                |

| 3   | RB_GPIO_PA10_IE | RW     | 1: Enable the corresponding interrupt;  | 0              |

|     |                 |        | 0: Disable the corresponding interrupt. |                |

|     |                 |        | PA6 pin interrupt enable bit:           |                |

| 2   | RB_GPIO_PA6_IE  | RW     | 1: Enable the corresponding interrupt;  | 0              |

|     |                 |        | 0: Disable the corresponding interrupt. |                |

|     |                 |        | PA4 pin interrupt enable bit:           |                |

| 1   | RB_GPIO_PA4_IE  | RW     | 1: Enable the corresponding interrupt;  | 0              |

|     |                 |        | 0: Disable the corresponding interrupt. |                |

|     |                 |        | PA3 pin interrupt enable bit:           |                |

| 0   | RB_GPIO_PA3_IE  | RW     | 1: Enable the corresponding interrupt;  | 0              |

|     |                 |        | 0: Disable the corresponding interrupt. |                |

## GPIO interrupt trigger mode register (R8\_GPIO\_INT\_MODE)

| Bit | Name            | Access | Description                            | Reset<br>value |

|-----|-----------------|--------|----------------------------------------|----------------|

|     |                 |        | PB10 pin interrupt mode selection bit: |                |

| 7   | RB_GPIO_PB10_IM | RW     | 1: Edge trigger;                       | 0              |

|     |                 |        | 0: Level trigger.                      |                |

|     |                 |        | PB4 pin interrupt mode selection bit:  |                |

| 6   | RB_GPIO_PB4_IM  | RW     | 1: Edge trigger;                       | 0              |

|     |                 |        | 0: Level trigger.                      |                |

|     |                 |        | PA12 pin interrupt mode selection bit: |                |

| 5   | RB_GPIO_PA12_IM | RW     | 1: Edge trigger;                       | 0              |

|     |                 |        | 0: Level trigger.                      |                |

|     |                 |        | PA11 pin interrupt mode selection bit: |                |

| 4   | RB_GPIO_PA11_IM | RW     | 1: Edge trigger;                       | 0              |

|     |                 |        | 0: Level trigger.                      |                |

| 3   | RB_GPIO_PA10_IM | RW     | PA10 pin interrupt mode selection bit: | 0              |

|   |                |    | 1: Edge trigger;                      |   |

|---|----------------|----|---------------------------------------|---|

|   |                |    | 0: Level trigger.                     |   |

|   |                |    | PA6 pin interrupt mode selection bit: |   |

| 2 | RB_GPIO_PA6_IM | RW | 1: Edge trigger;                      | 0 |

|   |                |    | 0: Level trigger.                     |   |

|   |                |    | PA4 pin interrupt mode selection bit: |   |

| 1 | RB_GPIO_PA4_IM | RW | 1: Edge trigger;                      | 0 |

|   |                |    | 0: Level trigger.                     |   |

|   |                |    | PA3 pin interrupt mode selection bit: |   |

| 0 | RB_GPIO_PA3_IM | RW | 1: Edge trigger;                      | 0 |

|   |                |    | 0: Level trigger.                     |   |

## GPIO interrupt polarity register (R8\_GPIO\_INT\_POLAR)

| Bit | Name            | Access | Description                                | Reset<br>value |

|-----|-----------------|--------|--------------------------------------------|----------------|

|     |                 |        | PB10 pin interrupt polarity selection bit: |                |

| 7   | RB_GPIO_PB10_IP | RW     | 1: High level/rising edge;                 | 0              |

|     |                 |        | 0: Low level/falling edge.                 |                |

|     |                 |        | PB4 pin interrupt polarity selection bit:  |                |

| 6   | RB_GPIO_PB4_IP  | RW     | 1: High level/rising edge;                 | 0              |

|     |                 |        | 0: Low level/falling edge.                 |                |

|     |                 |        | PA12 pin interrupt polarity selection bit: |                |

| 5   | RB_GPIO_PA12_IP | RW     | 1: High level/rising edge;                 | 0              |

|     |                 |        | 0: Low level/falling edge.                 |                |

|     |                 |        | PA11 pin interrupt polarity selection bit: |                |

| 4   | RB_GPIO_PA11_IP | RW     | 1: High level/rising edge;                 | 0              |

|     |                 |        | 0: Low level/falling edge.                 |                |

|     |                 |        | PA10 pin interrupt polarity selection bit: |                |

| 3   | RB_GPIO_PA10_IP | RW     | 1: High level/rising edge;                 | 0              |

|     |                 |        | 0: Low level/falling edge.                 |                |

|     |                 |        | PA6 pin interrupt polarity selection bit:  |                |

| 2   | RB_GPIO_PA6_IP  | RW     | 1: High level/rising edge;                 | 0              |

|     |                 |        | 0: Low level/falling edge.                 |                |

|     |                 |        | PA4 pin interrupt polarity selection bit:  |                |

| 1   | RB_GPIO_PA4_IP  | RW     | 1: High level/rising edge;                 | 0              |

|     |                 |        | 0: Low level/falling edge.                 |                |

|     |                 |        | PA3 pin interrupt polarity selection bit:  |                |

| 0   | RB_GPIO_PA3_IP  | RW     | 1: High level/rising edge;                 | 0              |

|     |                 |        | 0: Low level/falling edge.                 |                |

## PA port direction setting register (R32\_PA\_DIR)

| Bit     | Name       | Access | Description                                                                                                                         | Reset<br>value |

|---------|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|----------------|

| [31:16] | Reserved   | RO     | Reserved.                                                                                                                           | 0              |

| [15:0]  | R32_PA_DIR | RW     | Current input/output direction control of PA<br>pin:<br>1: The pin direction is output mode;<br>0: The pin direction is input mode. | 0              |

| Bit     | Name       | Access | Description                                                                                                                                                                                                                                | Reset<br>value |

|---------|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| [31:16] | Reserved   | RO     | Reserved.                                                                                                                                                                                                                                  | 0              |

| [15:0]  | R32_PA_PIN | RO     | <ul> <li>PA pin level status:</li> <li>1: The pin inputs high level;</li> <li>0: The pin inputs low level;</li> <li>The value of this bit is valid only when the corresponding bit of the direction register (R32_PA_DIR) is 0.</li> </ul> | 0              |

## PA port output data register (R32\_PA\_OUT)

| Bit     | Name       | Access | Description                                                                                                                                                                                                                                         | Reset<br>value |

|---------|------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| [31:16] | Reserved   | RO     | Reserved.                                                                                                                                                                                                                                           | 0              |

| [15:0]  | R32_PA_OUT | RW     | <ul> <li>PA pin output level status:</li> <li>1: The pin outputs high level;</li> <li>0: The pin outputs low level;</li> <li>The value of this bit is valid only when the corresponding bit of the direction register (R32_PA_DIR) is 1.</li> </ul> | 0              |

PA port bit clear register (R32\_PA\_CLR)

| Bit     | Name       | Access | Description                        | Reset<br>value |

|---------|------------|--------|------------------------------------|----------------|

| [31:16] | Reserved   | RO     | Reserved.                          | 0              |

|         |            |        | PA hold/clear data output control: |                |

| [15:0]  | R32_PA_CLR | WZ     | 1: The pin outputs low level;      | 0              |

|         |            |        | 0: No effect.                      |                |

## PA port pull-up configuration register (R32\_PA\_PU)

| Bit     | Name      | Access | Description                             | Reset<br>value |

|---------|-----------|--------|-----------------------------------------|----------------|

| [31:16] | Reserved  | RO     | Reserved.                               | 0              |

|         |           |        | PA pin pull-up function enable control: |                |

| [15:0]  | R32_PA_PU | RW     | 1: Enable pin pull-up function;         | 0              |

|         |           |        | 0: Disable pin pull-up function.        |                |

## PA port open-drain output and input pull-down configuration register (R32\_PA\_PD)

| Bit     | Name      | Access | Description                                                                                                                                                                                                                                                                                                      | Reset<br>value |

|---------|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| [31:16] | Reserved  | RO     | Reserved.                                                                                                                                                                                                                                                                                                        | 0              |

| [15:0]  | R32_PA_PD | RW     | <ul> <li>When the corresponding bit of direction register</li> <li>(R32_PA_DIR) is configured as 1 (ie output mode):</li> <li>1: Enable open-drain output function of this pin;</li> <li>1: Disable open-drain output function of this pin.</li> <li>When the corresponding bit of direction register</li> </ul> | 0              |

| (R32_PA_DIR) is configured as 0 (ie input mode): |  |

|--------------------------------------------------|--|

| 1: Enable the pull-down function of this pin;    |  |

| 1: Disable the pull-down function of this pin;   |  |

## PA port drive capability configuration register (R32\_PA\_DRV)

| Bit     | Name       | Access | Description                             | Reset<br>value |

|---------|------------|--------|-----------------------------------------|----------------|

| [31:16] | Reserved   | RO     | Reserved.                               | 0              |

| 54 5 63 |            |        | PA pin output drive capability control: | <u>^</u>       |

| [15:0]  | R32_PA_DRV | RW     | 1: The maximum drive current is 16mA;   | 0              |

|         |            |        | 0: The maximum drive current is 8mA.    |                |

## PA port Schmitt trigger enable configuration register (R32\_PA\_SMT):

| Bit     | Name       | Access | Description                                                                                                                          | Reset<br>value |

|---------|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|----------------|

| [31:16] | Reserved   | RO     | Reserved.                                                                                                                            | 0              |

|         |            |        | <ul><li>PA pin Schmitt trigger function control:</li><li>1: Enable the Schmitt trigger input function or</li></ul>                   |                |

| [15:0]  | R32_PA_SMT | RW     | low slope output function of this pin;<br>0: Disable the Schmitt trigger input function or<br>low slope output function of this pin. | 0              |

## PB port direction setting register (R32\_PB\_DIR)

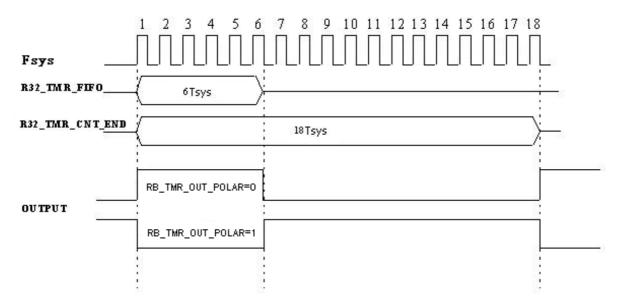

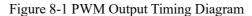

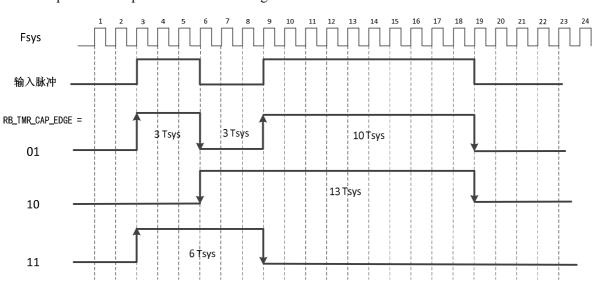

| Bit     | Name       | Access | Description                                                                               | Reset<br>value |